NanoXplore Software update NXmap v3

- Home

- /

- POSTS

- /

- Technology

- /

- NanoXplore Software update NXmap...

NanoXplore new Major Software update NXmap v3 available now NXmap is the main tool of NanoXplore design suite..

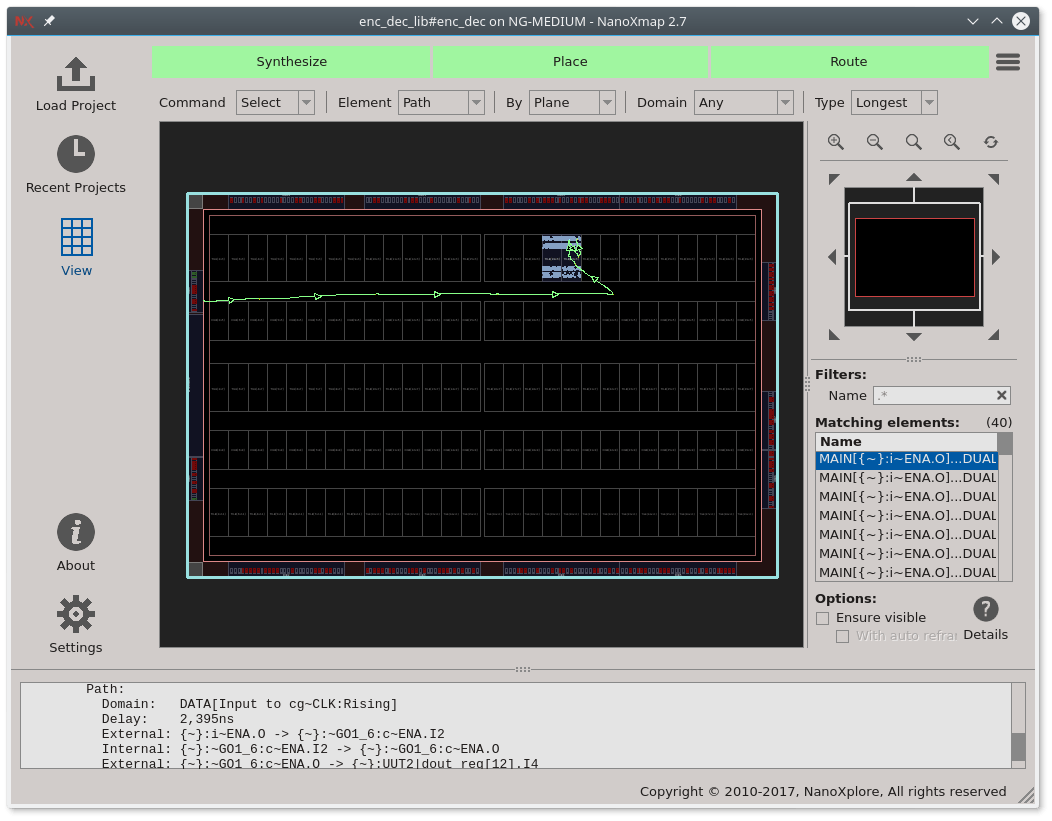

NXmap is the main tool of NanoXplore design suite. It allows user to perform the design flow to program a FPGA including, synthesis, place, route, static timing analysis and bitstream generation. NXmap consists in a set of C++ libraries that can be controlled either through a graphic user interface or through a Python wrapper for scripting.

NXcore

NXcore is a graphical user interface that presents all IP cores available for NanoXplore FGPA families. In addition to presenting each IP core and linking to the provider company, NXcore allows user to graphically define the parameters of some IP cores and generate the preconfigured and encrypted VHDL code that can be used as input of NXmap.

NXscope

NXscope is an embedded logic analyzer. It allows to sample a collection of internal data synchronously with a user’s clock (rising edge sensitive) and analyze the sampled results in a waveform viewer. NXscope is a NanoXplore IP Core. It’s generated by using the NXcore generator. The capture process is controlled by JTAG via the ANGIE USB-JTAG adapter with commands supported by NXbase2 software or NXboard GUI. The results can be displayed and analyzed either with :

- ModelSim wafeform viewer (using a simple testbench to read the .txt file generated by NXcore generator and display the waveforms).

- GTKWave (free waveform display tool)

NXbase2 & NXboard

NXbase2 is a command-line tool that can interact with evaluation kit boards for NanoXplore’s chips. It provides a way to upload bitstream files into the chip and is able to control some of the hardware features of the related evaluation kits. The communication between computer and evaluation kit board is done by JTAG via the ANGIE USB-JTAG adapter provided with the evaluation kit board. NXboard is a graphical user interface, using NXbase2, that allows easy interaction with the evaluation kit boards.

Features

nxmap and nxpython binaries are renamed in nxmap3 and nxpython3 respectively (links on old names are still present

temporary) General improvement and enhancement of the full NXmap compilation algorithm.

GUI improvements:

▪ Add Home page

▪ New Create Project page

▪ New pads configuration page

▪ New Timing Analysis page

▪ New Inspector command

▪ New Aperture and Focus edit commands

▪ New constraints display page (synthesis and placement)

▪ Remarks, Warnings and Errors are displayed

▪ More tooltips added to give help inside tool

▪ New addDSPLocation() and addRAMLocation() method Timing Analysis:

▪ Complete timing reports

▪ Timing constraints

▪ Timing analysis for PLL in NG-MEDIUM and NG-LARGE

▪ Limited maximum frequency for DSP, RAM and DFF

▪ Derating available for NG-MEDIUM and NG-LARGE: Best/Worst case analysis condition (voltage and temperature)

▪ Complete bitstream generation for NG-MEDIUM and NG-LARGE (EMBEDDED variants too)

▪ Simulator object available

▪ Adding documentation for progress method

▪ Python documentation updated

NanoXplore has developed Radiation-Hardened By Design SRAM-based FPGA devices for harsh environments applications.

By nature, SRAM-based FPGAs are volatile. NanoXplore has developed a dedicated architecture based on hardening techniques such as

- DICE (Dual Interlocked storage CEll) memory latch. DICE architecture has been used for Configuration Memory Cells and Internal registers (DFFs)

- EDAC for BRAM blocks

- TMR (Triple Module Redundancy) for all other blocks

Based on this hardening approach, our rad-hard SRAM FPGA are much more reliable than traditional SRAM FPGA in harsh environment.

To even furhter improve the reliability of our FPGA, NanoXplore has developped an advanced Configuration Memory Integrity Check (“CMIC”). CMIC is an internal scrubber controller based on a Finite State Machine with its own hardened memory block to store CRC signatures. The CMIC will constantly verify the integrity of the bitstream and any potnential single errors will be detected and corrected.

-

NG-Medium is a low-end RHBD FPGA device. Its P/N is NX1H35AS.

-

NG-Large is a mid-end RHBD FPGA device. Its P/N is NX1H140TSP.

-

NG-Ultra is a high-end RHBD FPGA device. Its P/N is NX2H540TSC.

Contacts : Montpellier

2196, Bd de la Lironde, 34980 Montferrier-sur-Lez

04 67 84 99 97

sales@nanoxplore.com

support@nanoxplore.com

MICROREL – Via delle Sassete n.33, CP.00065 – Fiano Romano, ROME, ITALY

Email: danilo.lauta@microrel.com

Phone : +39 334 9529414

Web: www.microrel.com

General Enquiries Email: info@microrel.com

D-85521 Ottobrunn-Riemerling, Germany

Phone: +49 (0)89 6602923

Email: sales@protec-semi.de

Web: www.protec-semi.de